# Chapter 5: Field–Effect Transistors

Robert Boylestad Digital Electronics

©2004 by Pearson Education

Slide 1

## FET

FET's (Field - Effect Transistors) are much like BJT's (Bipolar Junction Transistors).

#### Similarities:

- Amplifiers

- · Switching devices

- Impedance matching circuits

#### **Differences:**

- FET's are voltage controlled devices whereas BJT's are current controlled devices.

- FET's also have a higher input impedance, but BJT's have higher gains.

- FET's are less sensitive to temperature variations and because of there construction they are more easily integrated on IC's.

- FET's are also generally more static sensitive than BJT's.

# **FET Types**

• JFET ~ Junction Field-Effect Transistor

• **MOSFET** ~ Metal-Oxide Field-Effect Transistor

- **D-MOSFET** ~ Depletion MOSFET

- **E-MOSFET**  $\sim$  Enhancement MOSFET

Robert Boylestad Digital Electronics

Slide 2

©2004 by Pearson Education

Slide 3

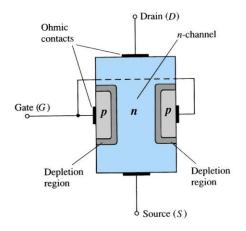

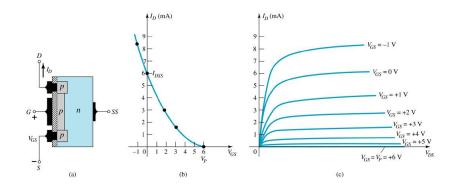

## **JFET Construction**

There are two types of JFET's: n-channel and p-channel. The n-channel is more widely used.

There are three terminals: Drain (D) and Source (S) are connected to n-channel

Robert Boylestad

Digital Electronics

C2004 by Pearson Education

## **Basic Operation of JFET**

JFET operation can be compared to a water spigot:

The source of water pressure – accumulated electrons at the negative pole of the applied voltage from Drain to Source The drain of water – electron deficiency (or holes) at the positive pole of the applied voltage from Drain to Source. The control of flow of water – Gate voltage that controls the width of the n-channel, which in turn controls the flow of electrons in the n-channel from source to drain. Robert Boylestad Digital Electronics (2004 by Person Education (2004 by Person (2004 by Person Education (2004 by Person (2004 by Person Education (2004 by Person (2004 by P

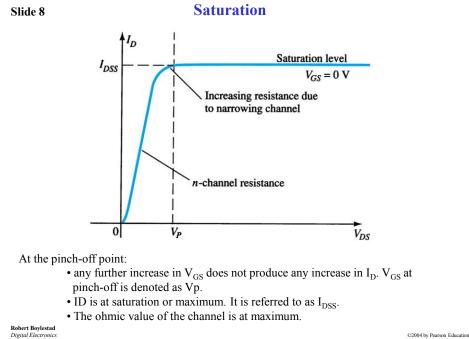

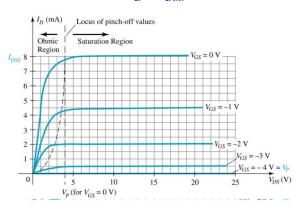

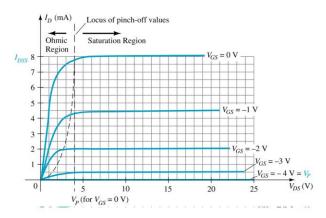

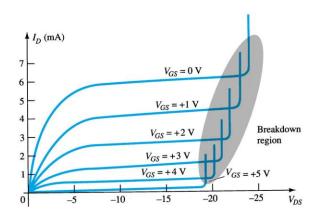

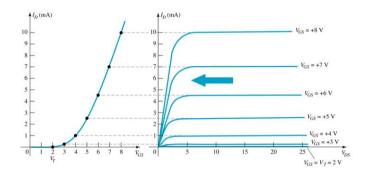

Slide 5 JFET Operating Characteristics

There are three basic operating conditions for a JFET:

- A.  $V_{GS} = 0$ ,  $V_{DS}$  increasing to some positive value

- B.  $V_{GS} < 0$ ,  $V_{DS}$  at some positive value

- C. Voltage-Controlled Resistor

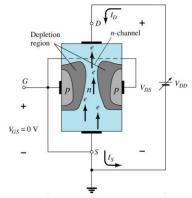

Slide 6 A.  $V_{GS} = 0$ ,  $V_{DS}$  increasing to some positive value

Three things happen when  $V_{GS} = 0$  and  $V_{DS}$  is increased from 0 to a more positive voltage:

- the depletion region between p-gate and n-channel increases as electrons from n-channel combine with holes from p-gate.

- increasing the depletion region, decreases the size of the n-channel which increases the resistance of the n-channel.

- But even though the n-channel resistance is increasing, the current  $(I_D)$  from

- Source to Drain through the n-channel is increasing. This is because  $V_{\text{DS}}$  is increasing.

Robert Boylestad Digital Electronics

©2004 by Pearson Education

Slide 7

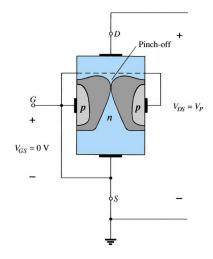

**Pinch-off**

If  $V_{GS} = 0$  and  $V_{DS}$  is further increased to a more positive voltage, then the depletion zone gets so large that it *pinches off* the n-channel. This suggests that the current in the n-channel (I<sub>D</sub>) would drop to 0A, but it does just the opposite: as  $V_{DS}$  increases, so does I<sub>D</sub>. **Robert Boylestad Robert Boylestad** (2004 by Pearson Education

Robert Boylestad Digital Electronics

Slide 9

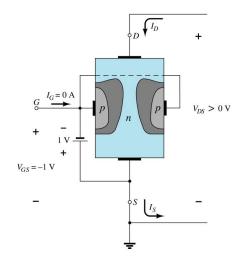

**B.**  $V_{GS} < 0$ ,  $V_{DS}$  at some positive value

As  $V_{\text{GS}}$  becomes more negative the depletion region increases.

Robert Boylestad Digital Electronics

#### As V<sub>GS</sub> becomes more negative:

- the JFET will pinch-off at a lower voltage (Vp).

- $I_D$  decreases ( $I_D < I_{DSS}$ ) even though  $V_{DS}$  is increased.

- Eventually  $I_D$  will reach 0A.  $V_{GS}$  at this point is called Vp or  $V_{GS(off)}$ .

- Also note that at high levels of  $V_{DS}$  the JFET reaches a breakdown situation.

- ID will increases uncontrollably if  $V_{DS} > V_{DSmax}$ .

Robert Boylestad Digital Electronics

©2004 by Pearson Education

Slide 11

## **C. Voltage-Controlled Resistor**

The region to the left of the pinch-off point is called the *ohmic region*. The JFET can be used as a variable resistor, where VGS controls the drain-source resistance (rd). As  $V_{GS}$  becomes more negative, the resistance (rd) increases.

$$=\frac{\mathbf{r}_{o}}{(1-\mathbf{V}_{GS}/\mathbf{V}_{P})^{2}}$$

rd

Robert Boylestad Digital Electronics

©2004 by Pearson Education

[Formula 5.1]

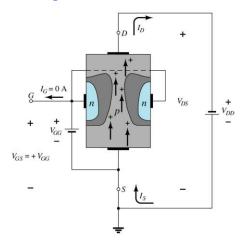

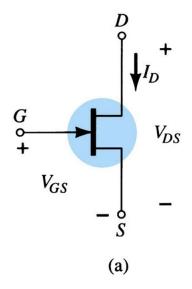

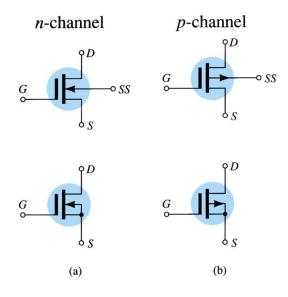

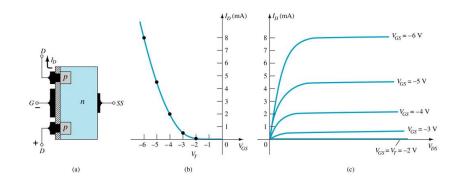

## **p-Channel JFETS**

p-Channel JFET acts the same as the n-channel JFET, except the polarities and currents are reversed.

Robert Boylestad Digital Electronics

Slide 12

©2004 by Pearson Education

Slide 13

**P-Channel JFET Characteristics**

As VGS increases more positively:

• the depletion zone increases

- $I_D$  decreases  $(I_D < I_{DSS})$  eventually  $I_D = 0A$

Also note that at high levels of VDS the JFET reaches a breakdown situation. ID increases uncontrollably if  $V_{DS} > V_{DSmax}$ .

Robert Boylestad Digital Electronics

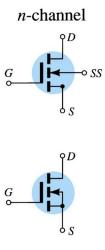

**JFET Symbols**

Robert Boylestad Digital Electronics

©2004 by Pearson Education

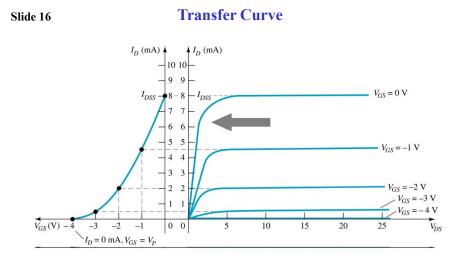

# Slide 15 Transfer Characteristics

The transfer characteristic of input-to-output is not as straight forward in a JFET as it was in a BJT.

In a BJT,  $\beta$  indicated the relationship between  $I_B$  (input) and  $I_C$  (output).

In a JFET, the relationship of  $V_{GS}$  (input) and  $I_{\rm D}$  (output) is a little more complicated:

$$I_D = I_{DSS} (1 - \frac{V_{GS}}{V_P})^2$$

[Formula 5.3]

Robert Boylestad Digital Electronics

From this graph it is easy to determine the value of I<sub>D</sub> for a given value of V<sub>GS</sub>.

Robert Boylestad Digital Electronics

©2004 by Pearson Education

# Slide 17 Plotting the Transfer Curve

Using  $I_{DSS}$  and Vp (V\_{GS(off)}) values found in a specification sheet, the Transfer Curve can be plotted using these 3 steps:

Step 1:

$$I_D = I_{DSS}(1 - \frac{V_{GS}}{V_P})^2$$

[Formula 5.3]Solving for  $V_{GS} = 0V$ : $I_D = I_{DSS} / V_{GS} = 0V$ [Formula 5.4]Step 2: $I_D = I_{DSS}(1 - \frac{V_{GS}}{V_P})^2$ [Formula 5.3]Solving for  $V_{GS} = Vp (V_{GS(off)})$ : $I_D = 0A / V_{GS} = V_P$ [Formula 5.5]Step 2: $I_D = 0A / V_{GS} = V_P$ [Formula 5.5]

Step 3:

Solving for

$$V_{GS} = 0V$$

to Vp:  $I_D = I_{DSS} (1 - \frac{V_{GS}}{V_P})^2$  [Formula 5.3]

Robert Boylestad Digital Electronics

# **Specification Sheet (JFETs)**

ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25 C unless otherwise noted) Characteristic Symbol Min Typ Max Unit

| OFF CHARACTERISTICS                                                                                                                                                          |        |                      |      |      |              |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------|------|------|--------------|------|

| Gate-Source Breakdown Voltage<br>$(I_G = -10 \ \mu Adc, V_{DS} = 0)$                                                                                                         |        | V <sub>(BR)GSS</sub> | 25   |      |              | Vdc  |

| $ \begin{array}{l} \mbox{Gate Reverse Current} \\ (V_{GS} = -15 \mbox{ Vdc}, V_{DS} = 0) \\ (V_{GS} = -15 \mbox{ Vdc}, V_{DS} = 0, T_A = 100^{\circ} \mbox{C}) \end{array} $ |        | 1 <sub>GSS</sub>     | ÷    | -    | -1.0<br>-200 | nAdc |

| Gate Source Cutoff Voltage<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 10 nAdc)                                                                                           | 2N5457 | V <sub>OS(off)</sub> | -0.5 | -    | -6.0         | Vdc  |

| Gate Source Voltage<br>(Vrs = 15 Vdc, In = 100 µAdc)                                                                                                                         | 2N5457 | V <sub>GS</sub>      | -    | -2.5 | -            | Vdc  |

5.0 mAdc

| Zero-Gate-Voltage Drain Current*<br>(V <sub>DS</sub> = 15 Vdc, V <sub>GS</sub> = 0) | 2N5457 | IDSS | 1.0 | 3.0 | T |

|-------------------------------------------------------------------------------------|--------|------|-----|-----|---|

| SMALL-SIGNAL CHARACTERISTICS                                                        |        |      |     |     |   |

|                                                                                     |        |      |     |     |   |

| Forward Transfer Admittance Common Source*<br>(V <sub>DS</sub> = 15 Vdc, V <sub>OS</sub> = 0, f = 1.0 kHz) 2N5457 | lynl  | 1000 | -   | 5000 | µmhos  |

|-------------------------------------------------------------------------------------------------------------------|-------|------|-----|------|--------|

| Output Admintance Common Source*<br>(V <sub>DS</sub> = 15 Vdc, V <sub>OS</sub> = 0, f = 1.0 kHz)                  | lYeal |      | 10  | 50   | jumhos |

| Input Capacitance<br>(V <sub>DS</sub> = 15 Vdc, V <sub>OS</sub> = 0, f = 1.0 MHz)                                 | Cas   |      | 4.5 | 7.0  | pF     |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 15 Vdc, V <sub>QS</sub> = 0, f = 1.0 MHz)                      | Cns   | 12   | 1.5 | 3.0  | pF     |

| Balas Tara Balas Webb of Killings Date Code of 1981                                                               |       |      |     | -    |        |

\*Pulse Test: Pulse Width 5 630 ms; Duty

Robert Boylestad Digital Electronics

Slide 18

©2004 by Pearson Education

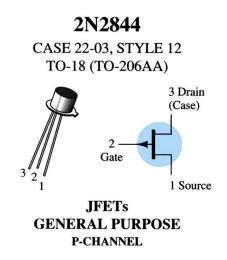

Slide 19 Case Construction and Terminal Identification

This information is also available on the specification sheet.

# Slide 20 Testing JFET

a. Curve Tracer - This will display the ID versus VDS graph for various levels of VGS.

b. Specialized FET Testers - These will indicate IDSS for JFETs.

Robert Boylestad Digital Electronics

©2004 by Pearson Education

Slide 21

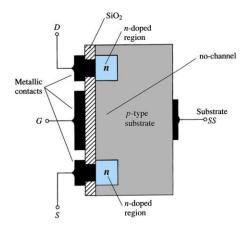

# **MOSFETs**

MOSFETs have characteristics similar to JFETs and additional characteristics that make then very useful.

There are 2 types:

• Depletion-Type MOSFET

• Enhancement-Type MOSFET

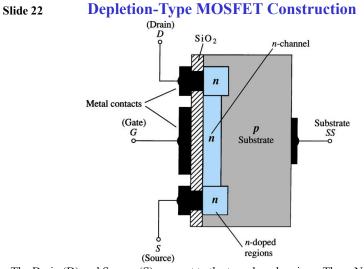

The Drain (D) and Source (S) connect to the to n-doped regions. These N-doped regions are connected via an n-channel. This n-channel is connected to the Gate (G) via a thin insulating layer of SiO<sub>2</sub>. The n-doped material lies on a p-doped substrate that may have an additional terminal connection called SS. Robert Boylestad Digital Electronics

©2004 by Pearson Education

#### Slide 23

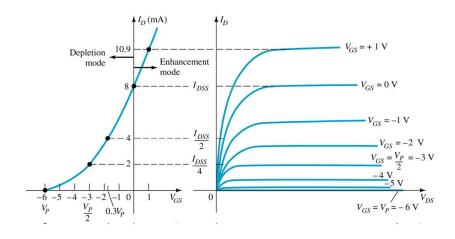

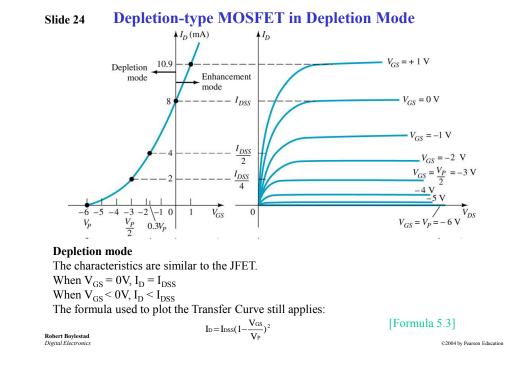

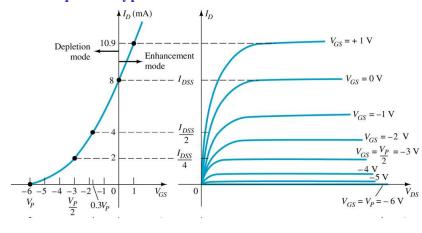

## **Basic Operation**

A Depletion MOSFET can operate in two modes: Depletion or Enhancement mode.

Robert Boylestad Digital Electronics

# Slide 25 Depletion-type MOSFET in Enhancement Mode

## Enhancement mode

$I_{D} = I_{DSS}(1 - \frac{V_{GS}}{V_{P}})^{2} \left[Formula 5.3\right]$

# p-Channel Depletion-Type MOSFET

The p-channel Depletion-type MOSFET is similar to the n-channel except that the voltage polarities and current directions are reversed.

Robert Boylestad Digital Electronics

©2004 by Pearson Education

Slide 27

**Symbols**

Robert Boylestad Digital Electronics

# **Specification Sheet**

| MAXIMUM RATINGS                                                                                                                         |             |                  |          |                      | CASE   | 2N379<br>22-03, 9<br>18 (TO-2 | STYLE 2    |       |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|----------|----------------------|--------|-------------------------------|------------|-------|

| Rating                                                                                                                                  | Symbol      | Value            | Unit     | 1                    | 11     | Gate                          | (F)        |       |

| Drain-Source Voltage<br>2N3797                                                                                                          | Vis         | 20               | Vdc      | ,                    | 11     | 20-                           | 1          |       |

| Gate-Source Voltage                                                                                                                     | VGS         | ±10              | Vdc      |                      |        |                               | 15         | OUTOP |

| Deain Current                                                                                                                           | Ip          | 20               | mAdc     |                      |        | MOSFE                         | Ts         |       |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C                                                                   | Po          | 200<br>1.14      | mW/mW/°C |                      |        | POWER                         |            | 0     |

| Junction Temperature Range                                                                                                              | TJ          | +175             | °C       | 1                    | N-CHA? | NEL - D                       | EPLETIC    | N     |

| Storage Charnel Temperature Range                                                                                                       | Teg         | -65 to +200      | °C.      |                      | 100000 | 1.1005-1.55                   | 0.0102000  |       |

| ELECTRICAL CHARACTERISTICS                                                                                                              |             | unless otherwise | e noted) |                      |        |                               |            |       |

| Chu                                                                                                                                     | racteristic |                  |          | Symbol               | Min    | Тур                           | Max        | Unit  |

| OFF CHARACTERISTICS                                                                                                                     |             |                  |          |                      |        |                               |            |       |

| Drain Source Breakdown Voltage<br>(V <sub>GS</sub> = -7.0 V, I <sub>D</sub> = 5.0 µA)                                                   |             |                  | N3797    | V <sub>IBREAX</sub>  | 20     | 25                            | -          | Vdc   |

| Gate Reverse Current (1)<br>$(V_{CS} = -10 \text{ V}, V_{DS} = 0)$<br>$(V_{CS} = -10 \text{ V}, V_{DS} = 0, T_A = 150^{\circ}\text{C})$ |             |                  |          | leas                 | 0      | 5                             | 1.0<br>200 | p.4.6 |

| Gate Source Cutoff Voltage<br>(ID = 2.0 µA, VDS = 10 V)                                                                                 |             |                  | IN3797   | V <sub>GS(eff)</sub> |        | -5.0                          | -7.0       | Vdc   |

| Deain-Gate Reverse Current (1)<br>(V <sub>DG</sub> = 10 V, I <sub>S</sub> = 0)                                                          |             |                  |          | 1000                 | 2      | 100                           | 1.0        | pAd   |

| ON CHARACTERISTICS                                                                                                                      |             |                  |          |                      |        | ()                            |            | 0     |

| Zero-Gase-Voltage Drain Current<br>(V <sub>ES</sub> = 10 V, V <sub>GS</sub> = 0)                                                        |             |                  | N3797    | loss                 | 2.0    | 2.9                           | 6.0        | mAd   |

| On-State Drain Current<br>(V <sub>DS</sub> = 10 V, V <sub>OS</sub> = +3.5 V)                                                            |             |                  |          | I <sub>Dire</sub>    |        |                               |            | mAd   |

| $(v_{DS} = 10 v, v_{OS} = 43.3 v)$                                                                                                      |             |                  | N3797    |                      | 9.0    | 14                            | 18         |       |

| SMALL-SIGNAL CHARACTERISTIC                                                                                                             | 8           |                  |          |                      |        |                               |            | -     |

| Forward Transfer Admittance                                                                                                             |             |                  |          | 1961                 |        |                               |            | µmba  |

| $(V_{CS} = 10 \text{ V}, V_{CS} = 0, f = 1.0 \text{ kHz})$                                                                              |             |                  | N3797    |                      | 1500   | 2300                          | 3000       |       |

| $(V_{\rm US}=10~V,~V_{\rm GS}=0,~f=1.0~{\rm MHz})$                                                                                      |             | -                | N3797    |                      | 1500   |                               |            |       |

| Output Admittance<br>(I <sub>DS</sub> = 10 V, V <sub>GS</sub> = 0, f = 1.0 kHz)                                                         |             |                  | N1797    | 17ml                 |        | 27                            | 60         | μnb   |

|                                                                                                                                         |             |                  |          | Can                  | -      | -/                            |            | pF    |

| Input Capacitance $(V_{DS}=10~V,~V_{GS}=0,~f=1.0~MHz)$                                                                                  |             |                  | N3797    | - ma                 |        | 6.0                           | 8.0        | pr    |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 10 V, V <sub>OS</sub> = 0, f = 1.0 MHz)                                              |             |                  |          | Cent                 | -      | 0.5                           | 0.8        | pF    |

| FUNCTIONAL CHARACTERISTICS                                                                                                              |             |                  |          |                      |        |                               |            |       |

| Noise Figure<br>(V <sub>DS</sub> = 10 V, V <sub>DS</sub> = 0, f = 1.0 kHz, R,                                                           | - 3 mopola  | 141              |          | NF                   | 10     | 3.8                           | -          | dB    |

Robert Boylestad Digital Electronics

Slide 28

©2004 by Pearson Education

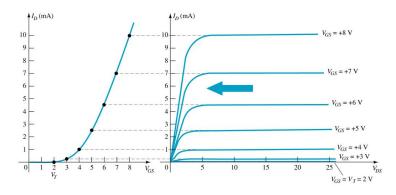

Slide 29 Enhancement-Type MOSFET Construction

The Drain (D) and Source (S) connect to the to n-doped regions. These n-doped regions are connected via an n-channel. The Gate (G) connects to the p-doped substrate via a thin insulating layer of  $SiO_2$ . There is no channel. The n-doped material lies on a p-doped substrate that may have an additional terminal connection called SS.

Robert Boylestad Digital Electronics

## **Basic Operation**

The Enhancement-type MOSFET only operates in the enhancement mode.

$\begin{array}{l} V_{GS} \text{ is always positive} \\ \text{As } V_{GS} \text{ increases, } I_{D} \text{ increases} \\ \text{But if } V_{GS} \text{ is kept constant and } V_{DS} \text{ is increased, then } I_{D} \text{ saturates } (I_{DSS}) \\ \text{The saturation level, } V_{DSsat} \text{ is reached.} \\ V_{Dsat} = V_{GS} - V_{T} \qquad \text{[Formula 5.12]} \end{array}$

Robert Boylestad Digital Electronics

Slide 31

**Transfer Curve**

To determine  $I_D$  given  $V_{GS}$ :  $I_D = k(V_{GS} - V_T)^2$  [Formula 5.13] where  $V_T$  = threshold voltage or voltage at which the MOSFET turns on. k = constant found in the specification sheet k can also be determined by using values at a specific point and the formula:

$$k = \frac{I_{D(on)}}{(V_{GS(ON)} - V_T)^2}$$

[Formula 5.14]

V<sub>DSsat</sub> can also be calculated:

$$V_{Dsat} = V_{GS} - V_T$$

Robert Boylestad Digital Electronics

©2004 by Pearson Education

[Formula 5.12]

# Slide 32 p-Channel Enhancement-Type MOSFETs

The p-channel Enhancement-type MOSFET is similar to the n-channel except that the voltage polarities and current directions are reversed.

Robert Boylestad Digital Electronics

©2004 by Pearson Education

Slide 33

# **Symbols**

(a)

Robert Boylestad Digital Electronics

# **Specification Sheet**

| MAXIMUM RATINGS                                                                                                                  |                                              |                 |            | 2N4351<br>CASE 20-03, STYLE 2<br>TO-72 (TO-206AF) |         |        |       |  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|------------|---------------------------------------------------|---------|--------|-------|--|

| Rating                                                                                                                           | Symbol                                       | Value           | Unit       | d a                                               |         | 3 Drai | 1     |  |

| Drain-Source Voltage                                                                                                             | Vos                                          | 25              | Vdc        | 1                                                 |         | -      |       |  |

| Drain-Gate Voltage                                                                                                               | Vno                                          | 30              | Vdc        | 1                                                 | 2       | lin -  | - 4   |  |

| Gate-Source Voltage*                                                                                                             | V <sub>GS</sub>                              | 30              | Vdc        | //                                                | Gate    | - P    | Case  |  |

| Drain Current                                                                                                                    | ID                                           | 30              | mAdc       | 12/1                                              |         | 1      |       |  |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C                                                            |                                              | 300<br>1.7      | mW<br>mW/C | 3 '4i<br>M                                        | OSFET   | 1 Sour | ce.   |  |

| Junction Temperature Range                                                                                                       | Ti                                           | 175             | °C.        | SWI                                               | TCHIN   | G      |       |  |

| Storage Temperature Range                                                                                                        | Tut                                          | -65 to +175     | 'C         | N-CHANNEL                                         | - ENHAL | NCEMEN | a c   |  |

| ELECTRICAL CHARACTERISTIC                                                                                                        | CS (T <sub>A</sub> = 25°C)<br>Tharacteristic | anless otherwis | e noted.)  | Symbol                                            | Min     | Max    | Unit  |  |

| Drain-Source Breakdown Voltage<br>(I <sub>D</sub> = 10 µA, V <sub>GS</sub> = 0)                                                  |                                              |                 |            | V <sub>(BR)DSX</sub>                              | 25      | -      | Vdc   |  |

| Zero-Gate-Voltage Drain Current<br>(V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 0) T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 150°C | loss                                         | -               | 10<br>10   | nAde<br>µAde                                      |         |        |       |  |

| Gate Reverse Carrent<br>(V <sub>GS</sub> = ± 15 Vdc, V <sub>DS</sub> = 0)                                                        |                                              |                 |            | l <sub>ass</sub>                                  | -       | ± 10   | pAde  |  |

| ON CHARACTERISTICS                                                                                                               |                                              |                 |            |                                                   |         |        | _     |  |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 10 µA)                                                       |                                              |                 |            | V <sub>GS(Th)</sub>                               | 1.0     | 5      | Vdc   |  |

| Drain-Source On-Voltage<br>(I <sub>D</sub> = 2.0 mA, V <sub>68</sub> = 10V)                                                      |                                              |                 |            | V <sub>EG(m)</sub>                                | 1       | 1.0    | v     |  |

| On-State Drain Current<br>(V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 10 V)                                                       |                                              |                 |            | I <sub>D(ot)</sub>                                | 3.0     | -      | mAd   |  |

| SMALL-SIGNAL CHARACTERIS                                                                                                         | rics                                         |                 |            |                                                   |         |        |       |  |

| Forward Transfer Admittance<br>(V <sub>DS</sub> = 10 V, I <sub>D</sub> = 2.0 mA, f = 1.0                                         | kHz)                                         |                 |            | y <sub>fs</sub>                                   | 1000    | -      | pamba |  |

| Input Capacitance<br>(V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 0, f = 140 kH                                                    | z)                                           |                 |            | Cisa                                              | (0)     | 5.0    | pF    |  |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 0, V <sub>GS</sub> = 0, f = 140 kHz)                                          |                                              | -               |            | C <sub>ns</sub>                                   | 100     | 1.3    | pF    |  |

| Drain-Substrate Capacitance<br>(V <sub>D(S)(B)</sub> = 10 V, f = 140 kHz)                                                        |                                              |                 |            | C <sub>d(sub)</sub>                               | -       | 5.0    | pF    |  |

| Drain-Source Resistance<br>(V <sub>GS</sub> = 10 V, I <sub>D</sub> = 0, f = 1.0 kHz)                                             |                                              |                 |            | Edu(on)                                           | ~       | 300    | ohme  |  |

| SWITCHING CHARACTERISTIC:                                                                                                        | \$                                           |                 |            |                                                   |         |        |       |  |

| Turn-On Delay (Fig. 5)                                                                                                           |                                              |                 |            | Li I                                              | -       | 45     | IIS   |  |

|                                                                                                                                  | mAdc, V <sub>DS</sub> = 1                    | 0 Vdc,          |            | L,                                                | -       | 65     | ns    |  |

| Turn-Off Delay (Fig. 7) (V <sub>GS</sub> = 1<br>(See Fig.                                                                        | 0 Vdc)<br>are 9; Times Ci                    | cuit Determine  | 1          | La2                                               | -       | 60     | ns    |  |

| Fall Time (Fig. 8)                                                                                                               | av a cases ca                                | con column      |            | t.                                                |         | 100    | 05    |  |

Robert Boylestad Digital Electronics

©2004 by Pearson Education

#### Slide 35

# **MOSFET Handling**

MOSFETs are very static sensitive. Because of the very thin  $SiO_2$  layer between the external terminals and the layers of the device, any small electrical discharge can stablish an unwanted conduction.

#### **Protection:**

- Always transport in a static sensitive bag

- Always wear a static strap when handling MOSFETS

- Apply voltage limiting devices between the Gate and Source, such as back-toback Zeners to limit any transient voltage.

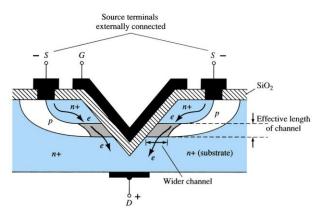

**VMOS**

## Slide 36

VMOS - Vertical MOSFET increases the surface area of the device.

#### Advantage:

- This allows the device to handle higher currents by providing it more surface area to dissipate the heat.

- VMOSs also have faster switching times.

Robert Boylestad Digital Electronics

©2004 by Pearson Education

#### Slide 37

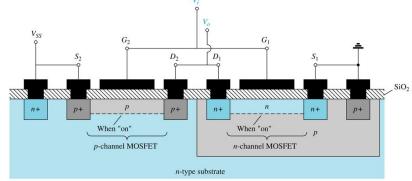

## **CMOS**

CMOS – Complementary MOSFET p-channel and n-channel MOSFET on the same substrate.

### Advantage:

- Useful in logic circuit designs

- Higher input impedance

- Faster switching speeds

- Lower operating power levels

Robert Boylestad Digital Electronics

©2004 by Pearson Education

Robert Boylestad Digital Electronics

Slide 38